Entwickler, die sich auf die Gestaltung von Leiterplatten (PCBs) für RJ45-Ethernet-Schnittstellen konzentrieren, stehen vor zahlreichen Herausforderungen. Diese umfassen Signalintegrität, ESD-Schutz und elektromagnetische Kompatibilität (EMC).

Um den Anforderungen gerecht zu werden, werden in diesem Artikel Schlüsselfaktoren und Praktiken vorgestellt, die während des Entwicklungsprozesses sorgfältig berücksichtigt werden sollten.

Signal Routing

Das Minimieren von Crosstalk und die Sicherstellung von geeignetem Matching innerhalb der Signalwege sind fundamentale Aspekte des Signal Routings auf PCBs. So müssen keine Signale kreuzen, es sei denn, sie sind durch eine Ground-Schicht effektiv isoliert. Traces sollten nach Möglichkeit length-matched sein, um konsistente Signallaufzeiten und damit eine hohe Signalqualität sicherzustellen. Ground-Vias sollten nahe an Signal-Vias platziert werden, um einen niedrigen Impedanzpfad zum Ground zu bieten.

Beim Entwurf einer Schnittstelle zwischen Media Access Control (MAC) und Physical Layer (PHY) auf einem Ethernet-Controller wird das Leiterbahndesign gemäß den MII- oder RMII-Standardprotokollen mit einer Punkt-zu-Punkt-Verbindung ausgeführt. Die Unterscheidung zwischen MII und RMII liegt primär in der Anzahl der Leitungen, die für die Kommunikation zwischen MAC und jedem PHY notwendig sind. Bei einem Gerät mit mehreren Ports können bestimmte Leitungen von MAC zu verschiedenen PHYs geteilt werden. Dennoch benötigt jedes PHY für MII 16 dedizierte Leitungen und für RMII 6 bis 7.

Um die Komplexität der Verkabelung zu reduzieren, wurde RMII ins Leben gerufen, welches die Leitungszahl um die Hälfte verringert. Ein essenzielles Bauteil in dieser Konfiguration ist der Taktgeber, der für die Synchronisierung von Übertragungs- und Empfangsaktionen zwischen MAC und PHY sorgt. Unter MII wird ein Takt von 2,5 MHz für 10 Mbps und 25 MHz für 100 Mbps verwendet. RMII hingegen nutzt einen durchgehenden 50-MHz-Takt für beide Geschwindigkeiten. Die Leitungen sollten einheitlich auf einer Schicht mit akkurater Längenabstimmung verlegt werden. Im Gegensatz zu anderen Standards können die Längentoleranzen bei TTL-Signalen großzügiger gehandhabt werden.

Beim Design der Verbindung zwischen PHY und RJ-45-Buchsen gelten striktere Richtlinien. Die Senden- (TX) und Empfangen- (RX) Bahnen sind als differenzielle Paare angelegt und müssen in ihrer Länge exakt angepasst und symmetrisch sein. Diese Pfade übertragen analoge Signale und sollten deshalb über eine analoge Ground-Fläche geführt werden. Eine durchdachte Mixed-Signal-Ground-Planung im Gerät ist daher unverzichtbar.

MDI Traces

MDI steht für "Media Dependent Interface" und bezieht sich auf die physischen Leiterbahnen auf einem PCB, die die Verbindung zwischen dem Ethernet-Transceiver (PHY) und dem RJ45-Anschluss, also der Ethernet-Buchse, herstellen. Diese Traces übertragen die differenziellen Signale der Ethernet-Datenkommunikation – die Transmit- (TX) und Receive- (RX) Signale.

In einem typischen Ethernet-Design umfassen MDI-Traces folgende Merkmale und Anforderungen:

- Differenzielle Paare: Die TX- und RX-Signale werden als differenzielle Paare geführt, um die Signalintegrität zu verbessern und elektromagnetische Interferenzen (EMI) sowie Crosstalk zu minimieren.

- Impedanzanpassung: MDI-Traces sind so gestaltet, dass sie eine charakteristische Impedanz von üblicherweise 100 Ohm differenziell aufweisen, mit einer Toleranz von ±10%. Dies ist wichtig, um Reflexionen zu minimieren und eine optimale Signalübertragung zu gewährleisten.

- Längenanpassung: Die Leiterbahnen müssen innerhalb bestimmter Toleranzen (oftmals innerhalb von 20 mils für 1 Gbps Übertragungen) längenangepasst sein, um sicherzustellen, dass die Signale gleichzeitig am Empfänger ankommen.

- Minimaler Einsatz von Vias und Stubs: Vias sind Durchkontaktierungen, die die Leiterbahnen von einer Schicht der PCB auf eine andere führen. Stubs sind überstehende Leiterbahnteile, die über das Anschlussziel hinausgehen. Beide können zu Impedanzänderungen, Reflexionen und Signalverlusten führen und sollten daher minimiert werden.

- Nähe zu Ground Planes: Um die Signalintegrität zu wahren, sollte ein Ground Plane (Massefläche) nahe an den MDI-Traces geführt werden, jedoch mit einem ausreichenden Abstand (oft 3*w oder mehr, wobei "w" die Breite der Trace ist), um unerwünschte kapazitive Kopplungen zu verhindern.

MII Traces

MII steht für "Media Independent Interface", eine standardisierte Schnittstelle, die die Verbindung zwischen einem Ethernet-MAC (Media Access Control) Layer und einem PHY (Physical Layer) Chip in Netzwerkgeräten wie Routern und Switches herstellt. Die MII-Schnittstelle erlaubt eine flexible Verbindung mit verschiedenen Arten von PHYs, unabhängig vom Übertragungsmedium, sei es Twisted-Pair-Kabel, Glasfaser oder etwas anderes.

Folgende Regeln gelten für MII-Traces auf einem PCB umfassen:

- Signallängen: Die Länge jeder MII-Leiterbahn sollte in der Regel unter 6 Zoll liegen, um Verzögerungen und Signalverluste zu minimieren. Die Gesamtlänge ist aufgrund der Zeitverzögerung und der potenziellen Signalintegritätsprobleme limitiert.

- Längenabgleich: Wie bei MDI-Traces müssen auch die MII-Traces in ihrer Länge innerhalb bestimmter Toleranzen abgeglichen sein (innerhalb von 20 mils für 1G Übertragungen und 50 mils für 100M oder 10M Übertragungen), um Timing-Probleme zu vermeiden.

- Single Ended Impedanz: Die einzelnen Leiterbahnen der MII-Schnittstelle sollten eine Impedanz von 50 Ohm aufweisen, mit einer Toleranz von ±10%. Diese Impedanzanpassung ist entscheidend für die Aufrechterhaltung der Signalintegrität.

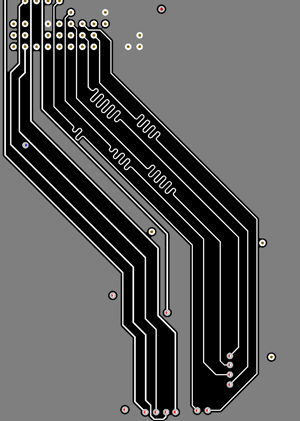

Typische length-matched diffpairs vom Prozessor-BGA (oben) zum Stecker auf isolierter Signal Plane

ESD-Risiken

ESD-Bedrohungen: ESD ist der Transfer von Ladungen zwischen Körpern mit unterschiedlichen Potenzialen, was häufig bei der direkten Berührung von Ethernet-Ports oder über die Luft geschehen kann. Der IEC61000-4-2-Standard definiert die Testverfahren für die ESD-Immunität von Geräten. ESD-Impulse treten als gemeinsame Modusereignisse (Common-Mode Events) im Bezug auf den GND (Erde) auf, was bedeutet, dass sie sich über die Erdverbindung in die Schaltung ausbreiten und Komponenten beschädigen können.

EFT-Bedrohungen: EFT, gemäß IEC61000-4-4-Standard, sind kurzzeitige Hochspannungsimpulse, die durch Schaltvorgänge in der Stromversorgung oder durch das Schalten induktiver Lasten verursacht werden. Diese können ähnliche Auswirkungen wie Common-Mode-Blitzeinschläge haben, bei denen alle Leiter im Verhältnis zum GND "überströmt" werden. Gut ausbalancierte Datenleitungen können Differentialenergie minimieren, aber die kapazitive Kopplung in Transformatoren kann immer noch Common-Mode-Energie zum Treiber übertragen.

CDE-Bedrohungen: CDE wird durch statische Aufladungen in Twisted-Pair-Kabeln verursacht und ist getrennt von ESD zu betrachten. CDEs können durch triboelektrische Effekte (Reibung) oder elektromagnetische Induktion entstehen und sehr hohe Spannungen erzeugen, die zu sehr zerstörerischen Entladungen führen können.

Ethernet-Transformer, ESD-Dioden und ihre Relevanz

ESD-Dioden bieten eine effektive Schutzmaßnahme gegen diese Bedrohungen. Sie sind in der Lage, hohe Spannungsspitzen sicher aufzufangen und schnell auf GND abzuleiten, bevor die Energie das Netzwerkgerät erreicht und Schaden anrichten kann. Durch ihre schnelle Reaktionszeit und die Fähigkeit, hohe Energiepegel zu bewältigen, sind ESD-Dioden besonders gut für den Schutz empfindlicher elektronischer Komponenten geeignet.

Diese Dioden sind so konzipiert, dass sie im Normalbetrieb hochohmig sind und keinen Einfluss auf das Signal haben. Wenn jedoch eine ESD-Spannungsspitze auftritt, werden sie sehr niederohmig und leiten die Überspannung ab. Für Ethernet-Anwendungen werden sie typischerweise in alle vier Kanäle für die Tx/Rx-Signalleitungen integriert, um vollständigen Schutz zu gewährleisten. Sie sind auch darauf ausgelegt, die Signalintegrität bei hohen Datenübertragungsraten nicht zu beeinträchtigen, indem sie eine niedrige Kapazität aufweisen, was insbesondere für Anwendungen wie Gigabit Ethernet entscheidend ist.

Die Verwendung von ESD-Dioden in Verbindung mit anderen Schutzmaßnahmen, wie ausreichendem Kriechabstand und Luftspalt auf PCBs und dem Einsatz von Isolationstransformatoren, kann dazu beitragen, ein robustes System zu schaffen, das gegen die gängigen elektrischen Bedrohungen in Ethernet-Umgebungen gerüstet ist.

Bezogen auf ESD-Schutz ist die Implementierung von ESD-Dioden für die Tx/Rx-Signalleitungen im RJ45-Konnektor unerlässlich. Bei Übertragungsgeschwindigkeiten, die bis zu 1 Gbps reichen können, ist besonders auf die Kapazität der ESD-Diode zu achten. Empfohlen wird eine Kapazität von <5 pF, insbesondere bei Gigabit Ethernet-Anwendungen, um die Signalintegrität nicht negativ zu beeinträchtigen. Unidirektionale ESD-Schutzgeräte werden aufgrund ihres überlegenen Schutzes in der negativen Richtung besonders empfohlen.

Der Ethernet-Transformer, auch bekannt als LAN-Übertrager, spielt eine entscheidende Rolle als Schnittstelle zwischen einem Netzwerkgerät und dem angeschlossenen Ethernetkabel. Er bietet eine essenzielle Sicherheitsfunktion durch die galvanische Trennung, die elektrische Isolation zwischen dem empfindlichen Innenleben elektronischer Geräte und dem externen Netzwerk sicherstellt. Diese Isolation schützt vor Spannungsspitzen und Störströmen, die durch das Kabel fließen könnten. Gleichzeitig muss der Übertrager eine fein abgestimmte Impedanzanpassung gewährleisten, um Signalreflexionen zu vermeiden und die Integrität der Datenübertragung zu erhalten. Trotz der anspruchsvollen Aufgabe, Signale bis zu einer Bandbreite von 1 Gbit/s zu übertragen, darf der Ethernet-Transformer das Sende- und Empfangssignal nur minimal dämpfen, um eine effiziente Kommunikation zu ermöglichen und die Leistungsfähigkeit des Netzwerks nicht zu beeinträchtigen. Die Qualität und das Design des LAN-Übertragers sind daher kritisch für die Leistungsfähigkeit der Netzwerkschnittstelle und die Zuverlässigkeit des gesamten Systems.

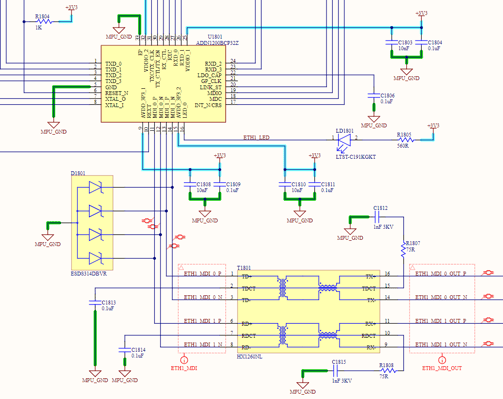

Folgendes Schematic zeigt die drei Komponenten PHY, Transformer und Protection Diodes im Zusammenschluss:

Schematics einer Verschaltung aus PHY, Transformer und ESD-Diodes

Schlussfolgerung

Abschließend lässt sich festhalten, dass die Entwicklung von ESD-konformen Ethernet-Schnittstellen mit RJ45-Steckern eine umfangreiche Berücksichtigung von Designprinzipien und Schutzmaßnahmen erfordert. Die Einhaltung der ESD-Normen wie der IEC61000-4-2 und der IEC61000-4-4 ist entscheidend für die Langlebigkeit und Zuverlässigkeit von Netzwerkgeräten. Ethernet-Schnittstellen sind häufigen ESD-Ereignissen ausgesetzt, welche durch Nutzerinteraktionen oder andere externe Quellen hervorgerufen werden können. Daher sind ESD-Schutzvorrichtungen, wie ESD-Dioden, ein kritischer Bestandteil im Designprozess. Die Anforderungen der Industriestandards und die Kenntnis der Umgebungsbedingungen spielen eine entscheidende Rolle im Designprozess. Die ESD-Sicherheit ist nicht nur eine Frage des Schutzes vor direkten Schäden, sondern auch ein Faktor der Nutzererfahrung, da sie die Verlässlichkeit und den wartungsfreien Betrieb von Netzwerkequipment unterstützt.

Die zunehmende Integration von Netzwerkfähigkeiten in eine Vielzahl von Geräten bedeutet, dass ESD-Schutz in den kommenden Jahren noch wichtiger wird. Die Einhaltung der Best Practices in Bezug auf ESD-Schutz trägt erheblich dazu bei, Produktausfälle zu vermeiden und die Kundenzufriedenheit zu steigern. Letztlich ist ein umsichtiges Design, das die potenziellen ESD-Bedrohungen für Ethernet-Schnittstellen angeht, ein entscheidender Schritt zur Gewährleistung der Gesamtzuverlässigkeit und Effizienz in der modernen elektronischen Kommunikation.

Kommentieren