ARM hat mit ARMv8-R eine Mikroarchitektur entwickelt, die Hardware-Virtualisierung, Echtzeitfähigkeit und Sicherheit kombiniert und so den wachsenden Ansprüchen der Automobilindustrie, der Industrie und der Medizintechnik gerecht wird. Diese Branchen benötigen zunehmend mehr Rechenleistung, sei es für ADAS (Advanced Driver Assistance Systems), Benutzerschnittstellen für Infotainment und Navigation oder für smarte Roboter und intelligente Medikamenten-Verteilungssysteme.

Im Gegensatz zur ARMv8-Architektur, die lediglich zwei Privileg-Modi kennt, wurde bei ARMv8-R eine zusätzliche Privileg-Ebene für einen echtzeitfähigen Virtual Machine Monitor (VMM) oder Hypervisor eingeführt. Dieser Hypervisor verwaltet parallel ein High-Level-Betriebssystem und ein RTOS, was eine flexiblere Nutzung der Hardware-Ressourcen ermöglicht. ARMv8-R basiert im Wesentlichen auf den Architekturen ARMv7/ARMv8-A, was den Übergang von der Konsumer- zur Embedded-Welt erleichtert und ermöglicht, dass alle Betriebssysteme, die dem 32-bit-A-Profil genügen, neben einem RTOS betrieben werden können.

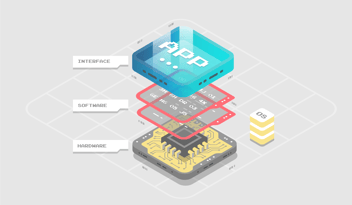

Die Virtualisierung schafft eine Abstraktionsschicht zwischen Betriebssystem und Hardware, sodass ein Betriebssystem glauben kann, es habe exklusive Kontrolle über die Hardware, während es tatsächlich innerhalb eines anderen Systems läuft. ARM hat eine zweistufige MPU-basierte Speicherumsetzung implementiert. Diese registerbasierte Übersetzung sorgt für zeitinvariante und deterministische Speicherzugriffe. Die erste Stufe, die als MMU wirkt, setzt virtuelle Adressen in physikalische Zwischenadressen (IPA) um, während die zweite Stufe, zugänglich nur für den Hypervisor, die IPAs in physikalische Adressen umsetzt. Dies stellt sicher, dass ein physikalischer Speicherzugriff ohne die Zustimmung des Hypervisors unmöglich ist.

Einteilung der Zugriffe auf IPAs über Hypervisor und MPU

ARMv8-R integriert auch Register für den Hypervisor-Modus, darunter das Exception Link Register (ELR), welches den Eintritt in den Hypervisor-Modus über Interrupts oder Systemfehler ermöglicht. Die Protected Memory System Architecture (PMSA) der Version 8 wurde verbessert, sodass Speicherregionen jetzt an jeder Adresse beginnen und enden können, die ein Vielfaches von 64 Byte darstellen.

VMM/ Hypervisior-Architektur auf ARMv8R

Die Interrupt-Verarbeitung in ARMv8-R ist so gestaltet, dass alle Interrupts an den Hypervisor geroutet werden können. Dieser führt eine Liste mit abzuarbeitenden Interrupts für jedes Gast-OS und verteilt sie über eine virtuelle CPU-Schnittstelle zur Abarbeitung an die jeweiligen Betriebssysteme. Die Möglichkeiten von ARMv8-R beinhalten auch die Unterstützung von SIMD-Operationen durch NEON, was insbesondere für Anwendungen in ADAS und Industrie von Vorteil ist.

Die Cortex-R52-Mikroarchitektur, die auf ARMv8-R basiert, bietet deterministische Echtzeit-Performance und hat eine dual-issue In-Order-Ausführungspipeline mit einer Länge von 8 Stufen. Diese Architektur wurde optimiert, um variable und nicht-deterministische Operationen zu vermeiden. Zur Unterstützung der Sicherheit bietet die R52 ECC über die Speicherbusse und den Speicher selbst sowie Multi-Core Lock Step, bei dem zwei R52-Kerne parallel dieselbe Aufgabe ausführen.

Zusammenfassung und Nutzen

Sichere, architektur-basierte Virtualisierung ist der Schlüssel dafür, dass in verteilten Systemen immer mehr Software-Funktionen in immer weniger elektronischen Steuergeräten bereitgestellt werden können. Virtualisierung ermöglicht es, verschiedene Software-Komponenten effizient und sicher auf einer gemeinsamen Hardware-Plattform zu betreiben, was zu einer besseren Ressourcennutzung und reduzierten Hardware-Kosten führt.

Durch die Trennung der Zugriffsebenen in deterministischer Software wird gleichzeitig die funktionale Sicherheit gewährleistet. Dies bedeutet, dass kritische und nicht-kritische Funktionen isoliert und unabhängig voneinander ausgeführt werden können, wodurch das Risiko von Fehlfunktionen und Sicherheitsverletzungen minimiert wird. So können sicherheitsrelevante Prozesse zuverlässig geschützt werden, während andere Anwendungen parallel und störungsfrei ablaufen.

Kommentieren