Safety Islands sind unabhängige Domänen innerhalb eines Systems-on-Chip (SoC), die eine hohe Fehlertoleranz von den restlichen Komponenten des Systems bieten. Dies wird durch separate Spannungs-, Takt- und Reset-Domänen sowie eigene dedizierte Peripheriegeräte und Ressourcen erreicht. Safety Islands können sicherheitskritische Funktionen weiterführen, selbst wenn ein Applikationsprozessor abstürzt, hängt oder zurückgesetzt werden muss. Sie bieten eine höhere Integration auf einem einzigen Siliziumchip, eine niedrigere Ausfallrate (FIT) und reduzieren den Platzbedarf auf der Leiterplatte. Allerdings können sie auch die eindeutige Bestimmung von abhängigen und gemeinsamen Ausfallmodi erschweren, was eine wichtige Anforderung für die funktionale Sicherheit darstellt.

Safety Islands übernehmen das Fehlermanagement und die Kontrolle über sicherheitskritische Funktionen des Systems, ermöglichen die Wiederherstellung komplexer Domänen und gewährleisten eine zuverlässige Echtzeit-Kommunikation innerhalb eines funktional sicheren Gesamtsystems. Außerdem sind sie in der Lage, Fehlerzustände an externe Systeme zu signalisieren, um eine angemessene Reaktion sicherzustellen.

Zu den besonderen Fähigkeiten von Safety Islands gehören dedizierte Rechen-, Speicher- und I/O-Ressourcen, die unabhängig vom Rest des Systems operieren. Sie arbeiten mit eigenen Takt- und Power-Domänen, was ihre Unabhängigkeit und Fehlertoleranz erhöht. Durch diese Isolation und spezielle Design-Prinzipien wird die Komplexität der sicherheitskritischen Funktionen reduziert. Selbst wenn der Rest des Systems ausfällt, bleiben die sicherheitskritischen Funktionen in der Safety Island intakt und betriebsbereit.

Implementierung von On-Chip-Funktionaler Sicherheit

Das Ziel der funktionalen Sicherheit ist es, zu verhindern, dass ein Ausfall eines sicherheitskritischen Systems Schaden verursacht. Funktionale Sicherheitsmechanismen schützen das Design vor Fehlern, indem sie sowohl latente als auch transiente Hardwarefehler erkennen. Die Abdeckung dieser Fehlerarten bestimmt den diagnostischen Gesamtabdeckungsgrad des Designs und damit die erreichbare SIL-Stufe. Häufig verwendete Sicherheitsmechanismen sind eingebettete Monitore, die strukturelle oder funktionale Defekte überwachen.

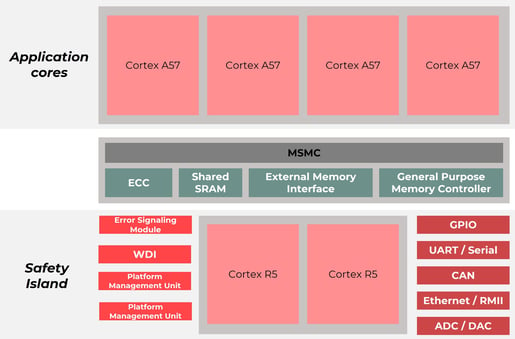

Das folgende Beispiel soll ein mögliches architektonisches Szenario darstellen, welches Sensor-Fusion-Algorithmen auf einem Mehrkern-Prozessor ausführt und gleichzeitig funktional sichere Aktuatorik, Kommunikation und I/O erfüllen soll.

Folgende Aufgabenteilung ist dann gegeben:

- der Mehrkern-Prozessor überprüft die Sensordaten.

- die Safety Island überwacht den Mehrkern-Prozessor

- die MCU innerhalb der Safety Island steuert die Aktuatoren.

- das MCU prüft, ob die Aktuatoren auf die Steuerung wie erwartet reagieren.

- ein externer PMIC überwacht die Hardware- und Softwareausführung des MCU.

- der PMIC überwacht den Betrieb der Hardware des Anwendungsprozessors.

PMICs haben typischerweise Enable- oder OV/UV-Pins, die zusätzlich den Gesamtsystemzustand an die Safety Island weitergeben. Mögliche Fehler, die mit dem PMIC abgefangen werden können, sind beispielsweise:

- Ausfälle der Versorgungsspannungen für das MCU oder das SoC

- Ausfall der Eingangsspannung zur PMICs

- Fehler in der Software oder Hardware des MCU

Wenn entweder der Prozessor oder das MCU in einem sicherheitskritischen System ausfallen, wird das System verschiedene Maßnahmen ergreifen, um die Sicherheit und Funktionalität so weit wie möglich aufrechtzuerhalten. Wenn der Prozessor ausfällt, erkennt die MCU diesen Zustand und kann entsprechende Maßnahmen ergreifen. Die MCU kann das System in einen sicheren Zustand versetzen, indem es die Aktuatoren so steuert, dass das Gerät oder die Maschine in einen sicheren Modus wechselt. Die MCU kann Fehler an externe Systeme signalisieren, sodass umliegende Systeme gewarnt werden und ebenfalls Gegenmaßnahmen einleiten.

Bei einem Ausfall von entweder SoC oder MCU werden dann entsprechend der Fehlertoleranz Maßnahmen für das Gesamtsystem definiert. Bei fehlertolerantem Verhalten werden die verbleibenden Komponenten die wichtigsten Sicherheitsfunktionen weiterhin erfüllen können. Umgekehrt wird im nichttoleranten Fall das gesamte System in einen sicheren Zustand versetzt

Zusammenfassung

Safety Islands verändern insofern die Landschaft möglicher Architekturen in der funktionalen Sicherheit, als dass innerhalb einer IC-Komponente mit Mehrkern-Prozessoren mit niedrigeren Sicherheitsanforderungen und Safety-Island-MCUs mit harter Isolation und konkreten Safe-State sowie Echtzeitanforderungen gemeinschaftlich verbaut sind. Insbesondere mit Blick auf die Software ändert das die Interkommunikations- sowie Isolations- und Schutzanforderungen merklich, eröffnet aber gleichzeitig eine Reihe an grundlegend neuen Anwendungsfeldern, bei denen schlussendlich Qualifikation und Sicherheitsbewertung vereinfacht werden können.

Kommentieren